Prabhat Mishra and Nikil D. Dutt FUNCTIONAL VERIFICATION OF PROGRAMMABLE EMBEDDED ARCHITECTURES A Top-Down Approach Springer

# Functional Verification of Programmable Embedded Architectures

A Top-Down Approach

# FUNCTIONAL VERIFICATION OF PROGRAMMABLE EMBEDDED ARCHITECTURES

#### A Top-Down Approach

#### PRABHAT MISHRA

Department of Computer and Information Science and Engineering University of Florida, USA

#### NIKIL D. DUTT

Center for Embedded Computer Systems Donald Bren School of Information and Computer Sciences University of California, Irvine, USA

Prabhat Mishra University of Florida USA Nikil D. Dutt University of California, Irvine USA

Functional Verification of Programmable Embedded Architectures A Top-Down Approach

ISBN 0-387-26143-5 ISBN 978-0387-26143-0 e-ISBN 0-387-26399-3 Printed on acid-free paper.

© 2005 Springer Science+Business Media, Inc.

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, Inc., 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed in the United States of America.

987654321

SPIN 11430100

springeronline.com

## **Contents**

| Preface |                 |                                             |    |

|---------|-----------------|---------------------------------------------|----|

| Ac      | Acknowledgments |                                             |    |

| I       | Intr            | roduction to Functional Verification        | 1  |

| 1       | Intr            | oduction                                    | 3  |

|         | 1.1             | Motivation                                  |    |

|         |                 | 1.1.1 Growth of Design Complexity           |    |

|         |                 | 1.1.2 Functional Verification - A Challenge |    |

|         | 1.2             | Traditional Validation Flow                 |    |

|         | 1.3             | Top-Down Validation Methodology             | 10 |

|         | 1.4             | Book Organization                           | 12 |

| II      | Ar              | chitecture Specification                    | 13 |

| 2       | Arcl            | hitecture Specification                     | 1: |

|         | 2.1             | Architecture Description Languages          | 10 |

|         |                 | 2.1.1 Behavioral ADLs                       | 13 |

|         |                 | 2.1.2 Structural ADLs                       | 19 |

|         |                 | 2.1.3 Mixed ADLs                            | 19 |

|         |                 | 2.1.4 Partial ADLs                          | 20 |

|         | 2.2             | ADLs and Other Specification Languages      | 20 |

|         | 2.3             | Specification using EXPRESSION ADL          | 2  |

|         |                 | 2.3.1 Processor Specification               |    |

|         |                 | 2.3.2 Coprocessor Specification             |    |

|         |                 | 2.3.3 Memory Subsystem Specification        |    |

|         | 2.4             | Chapter Summary                             | 23 |

viii CONTENTS

| 3  | Vali | dation of Specification                             | 29 |

|----|------|-----------------------------------------------------|----|

|    | 3.1  | Validation of Static Behavior                       | 30 |

|    |      | 3.1.1 Graph-based Modeling of Pipelines             | 31 |

|    |      | 3.1.2 Validation of Pipeline Specifications         | 34 |

|    |      | 3.1.3 Experiments                                   | 45 |

|    | 3.2  | Validation of Dynamic Behavior                      | 48 |

|    |      | 3.2.1 FSM-based Modeling of Processor Pipelines     | 48 |

|    |      | 3.2.2 Validation of Dynamic Properties              | 54 |

|    |      | 3.2.3 A Case Study                                  | 59 |

|    | 3.3  | Related Work                                        | 61 |

|    | 3.4  | Chapter Summary                                     | 62 |

|    |      |                                                     |    |

| II | I To | op-Down Validation                                  | 63 |

| 4  | Exe  | cutable Model Generation                            | 65 |

|    | 4.1  | Survey of Contemporary Architectures                | 66 |

|    |      | 4.1.1 Summary of Architectures Studied              | 66 |

|    |      | 4.1.2 Similarities and Differences                  | 68 |

|    | 4.2  | Functional Abstraction                              | 69 |

|    |      | 4.2.1 Structure of a Generic Processor              | 69 |

|    |      | 4.2.2 Behavior of a Generic Processor               | 73 |

|    |      | 4.2.3 Structure of a Generic Memory Subsystem       | 74 |

|    |      | 4.2.4 Generic Controller                            | 74 |

|    |      | 4.2.5 Interrupts and Exceptions                     | 75 |

|    | 4.3  | Reference Model Generation                          | 77 |

|    | 4.4  | Related Work                                        | 80 |

|    | 4.5  | Chapter Summary                                     | 81 |

| 5  | Desi | ign Validation                                      | 83 |

|    | 5.1  | Property Checking using Symbolic Simulation         | 85 |

|    | 5.2  | Equivalence Checking                                | 87 |

|    | 5.3  | Experiments                                         | 88 |

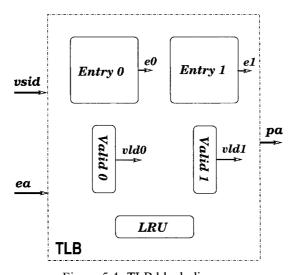

|    |      | 5.3.1 Property Checking of a Memory Management Unit | 88 |

|    |      | 5.3.2 Equivalence Checking of the DLX Architecture  | 91 |

|    | 5.4  | Related Work                                        | 92 |

|    | 5.5  | Chapter Summary                                     | 93 |

| CONTENTS | ix |

|----------|----|

|          |    |

| 6                          | <b>Functional Test Generation</b>              | 95  |  |  |

|----------------------------|------------------------------------------------|-----|--|--|

|                            | 6.1 Test Generation using Model Checking       | 95  |  |  |

|                            | 6.1.1 Test Generation Methodology              | 96  |  |  |

|                            | 6.1.2 A Case Study                             | 99  |  |  |

|                            | 6.2 Functional Coverage driven Test Generation | 103 |  |  |

|                            | 6.2.1 Functional Fault Models                  | 103 |  |  |

|                            | 6.2.2 Functional Coverage Estimation           | 105 |  |  |

|                            | 6.2.3 Test Generation Techniques               | 106 |  |  |

|                            | 6.2.4 A Case Study                             | 112 |  |  |

|                            | 6.3 Related Work                               | 116 |  |  |

|                            | 6.4 Chapter Summary                            | 117 |  |  |

| IV                         | Future Directions                              | 119 |  |  |

| 7                          | Conclusions                                    | 121 |  |  |

| ′                          | 7.1 Research Contributions                     | 121 |  |  |

|                            | 7.2 Future Directions                          | 121 |  |  |

|                            | 7.2 Tutule Directions                          | 122 |  |  |

| V                          | Appendices                                     | 125 |  |  |

| A                          | Survey of Contemporary ADLs                    | 127 |  |  |

|                            | A.1 Structural ADLs                            | 127 |  |  |

|                            | A.2 Behavioral ADLs                            | 130 |  |  |

|                            | A.3 Mixed ADLs                                 | 134 |  |  |

|                            | A.4 Partial ADLs                               | 139 |  |  |

| В                          | Specification of DLX Processor                 | 141 |  |  |

| C                          | Interrupts & Exceptions in ADL                 | 147 |  |  |

| D                          | Validation of DLX Specification                | 151 |  |  |

| E Design Space Exploration |                                                | 155 |  |  |

|                            | E.1 Simulator Generation and Exploration       | 156 |  |  |

|                            | E.2 Hardware Generation and Exploration        | 162 |  |  |

| Re                         | References                                     |     |  |  |

| Inc                        | Index                                          |     |  |  |

## **List of Figures**

| 1.1  | An example embedded system                                          | 4  |

|------|---------------------------------------------------------------------|----|

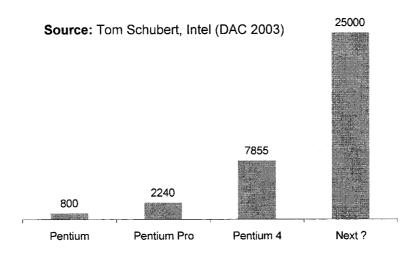

| 1.2  | Exponential growth of number of transistors per integrated circuit  | 5  |

| 1.3  | North America re-spin statistics                                    | 6  |

| 1.4  | Complexity matters                                                  | 7  |

| 1.5  | Pre-silicon logic bugs per generation                               | 8  |

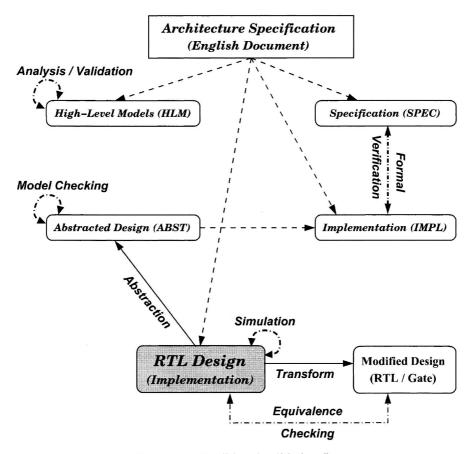

| 1.6  | Traditional validation flow                                         | 9  |

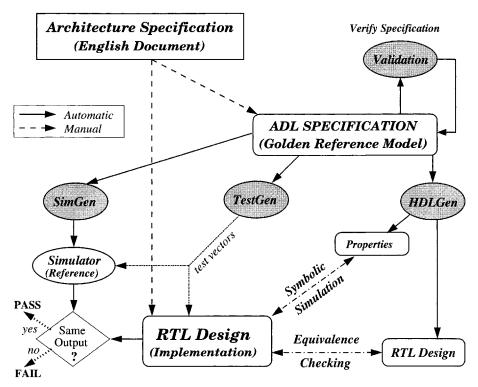

| 1.7  | Proposed specification-driven validation methodology                | 11 |

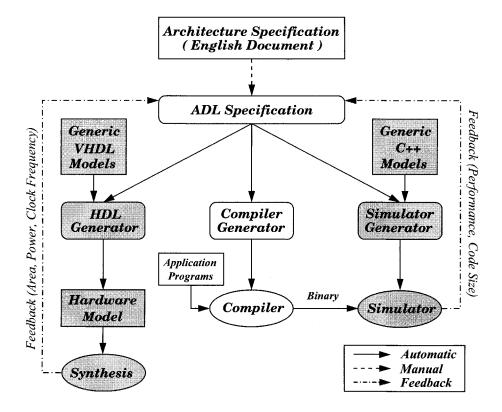

| 2.1  | ADL-driven exploration and validation of programmable architec-     |    |

|      | tures                                                               | 16 |

| 2.2  | Taxonomy of ADLs                                                    | 17 |

| 2.3  | Commonality between ADLs and non-ADLs                               | 21 |

| 2.4  | Block level description of an example architecture                  | 22 |

| 2.5  | Pipeline level description of the DLX processor shown in Figure 2.4 | 23 |

| 2.6  | Specification of the processor structure using EXPRESSION ADL       | 24 |

| 2.7  | Specification of the processor behavior using EXPRESSION ADL        | 25 |

| 2.8  | Coprocessor specification using EXPRESSION ADL                      | 26 |

| 2.9  | Memory subsystem specification using EXPRESSION ADL                 | 27 |

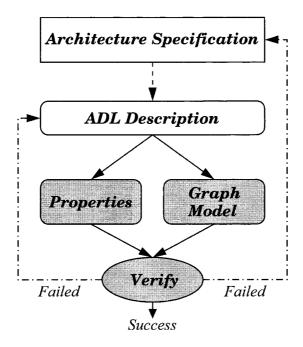

| 3.1  | Validation of pipeline specifications                               | 30 |

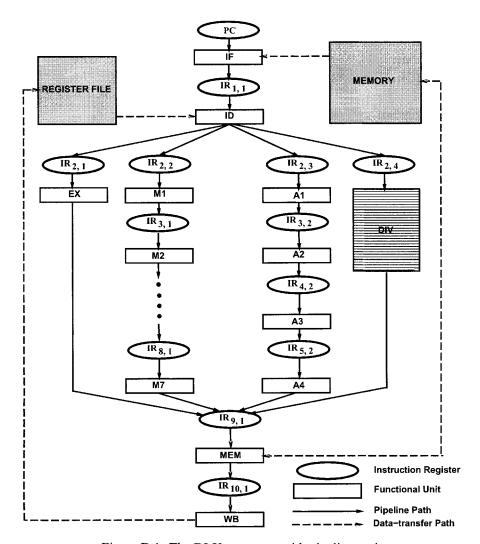

| 3.2  | An example architecture                                             | 32 |

| 3.3  | A fragment of the behavior graph                                    | 33 |

| 3.4  | An example processor with false pipeline paths                      | 36 |

| 3.5  | An example processor with false data-transfer paths                 | 37 |

| 3.6  | The DLX architecture                                                | 46 |

| 3.7  | ADL driven validation of pipeline specifications                    | 49 |

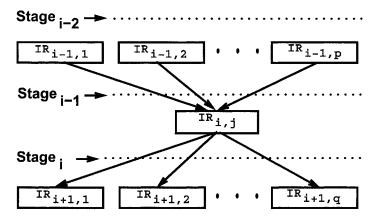

| 3.8  | A fragment of a processor pipeline                                  | 50 |

| 3.9  | The processor pipeline with only instruction registers              | 51 |

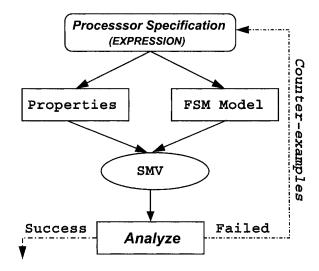

| 3.10 | Automatic validation framework using SMV                            | 59 |

xii LIST OF FIGURES

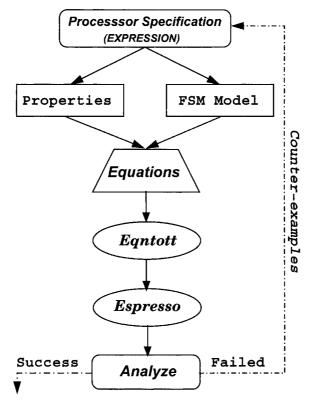

| 3.11 | Automatic validation framework using equation solver        | 60  |

|------|-------------------------------------------------------------|-----|

| 4.1  | A fetch unit example                                        | 70  |

| 4.2  | Modeling of RenameRegister function using sub-functions     | 72  |

| 4.3  | Modeling of MAC operation                                   | 73  |

| 4.4  | Modeling of associative cache function using sub-functions  | 74  |

| 4.5  | Example of distributed control                              | 75  |

| 4.6  | Example of centralized control                              | 76  |

| 4.7  | Mapping between MACcc and generic instructions              | 78  |

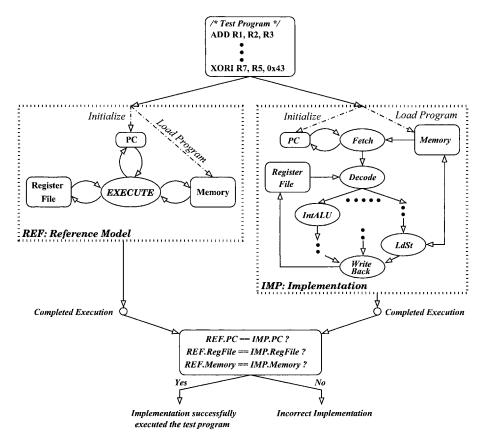

| 4.8  | Simulation model generation for the DLX architecture        | 79  |

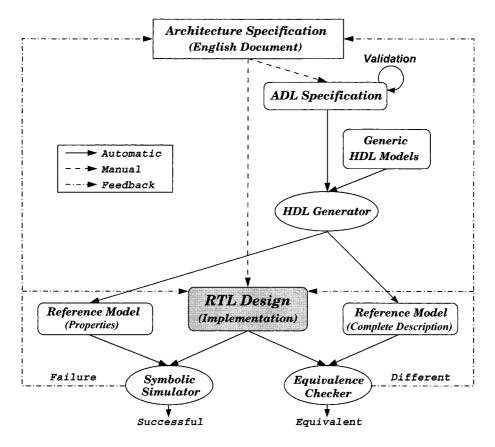

| 5.1  | Top-down validation methodology                             | 84  |

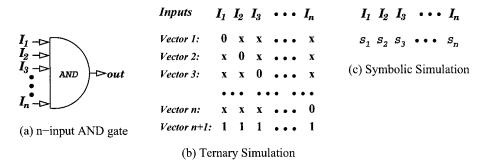

| 5.2  | Test vectors for validation of an AND gate                  | 85  |

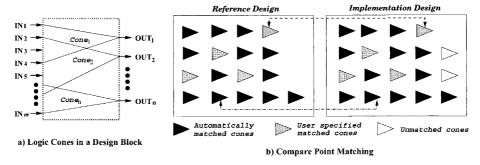

| 5.3  | Compare point matching between reference and implementation |     |

|      | design                                                      | 87  |

| 5.4  | TLB block diagram                                           | 89  |

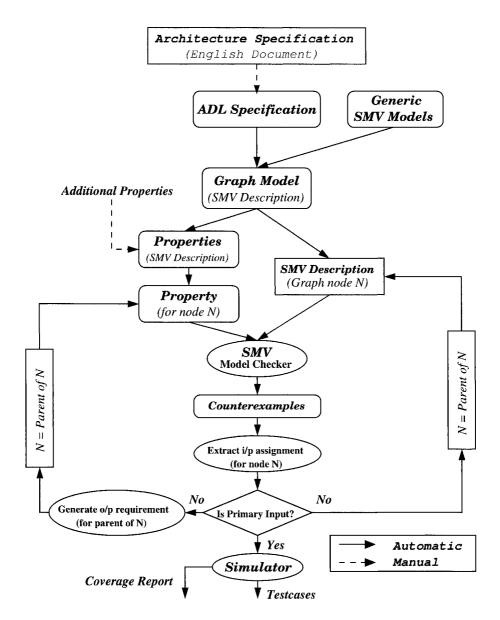

| 6.1  | Test program generation methodology                         | 97  |

| 6.2  | A fragment of the DLX architecture                          | 100 |

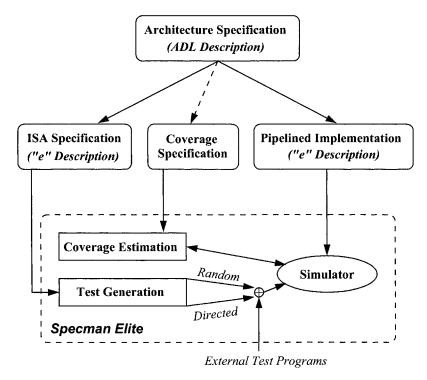

| 6.3  | Test Generation and Coverage Estimation                     | 112 |

| 6.4  | Validation of the Implementation                            | 114 |

| C.1  | Specification of division_by_zero exception                 | 148 |

| C.2  | Specification of illegal_slot_instruction exception         | 148 |

| C.3  | Specification of machine_reset exception                    | 149 |

| C.4  | Specification of interrupts                                 | 149 |

| D.1  | The DLX processor with pipeline registers                   | 152 |

| E.1  | Architecture exploration framework                          | 156 |

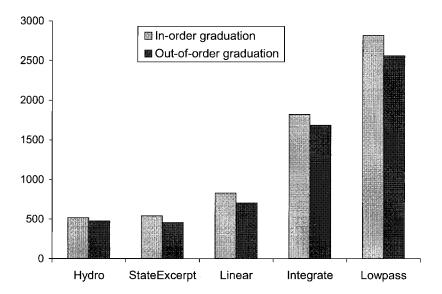

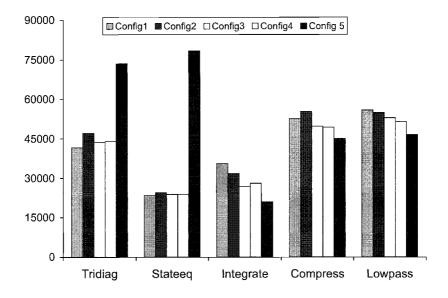

| E.2  | Cycle counts for different graduation styles                | 158 |

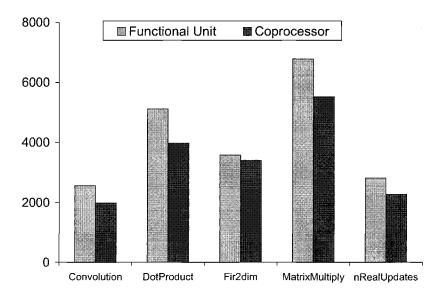

| E.3  | Functional unit versus coprocessor                          | 160 |

| E.4  | Cycle counts for the memory configurations                  | 162 |

| E.5  | The application program                                     | 163 |

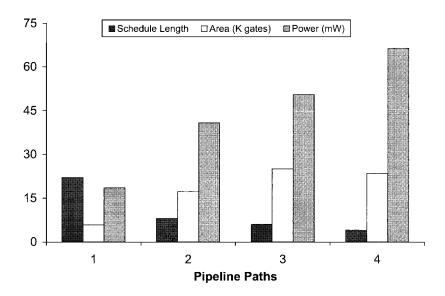

| E.6  | Pipeline path exploration                                   | 164 |

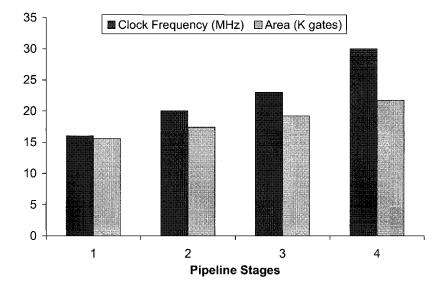

| E.7  | Pipeline stage exploration                                  | 165 |

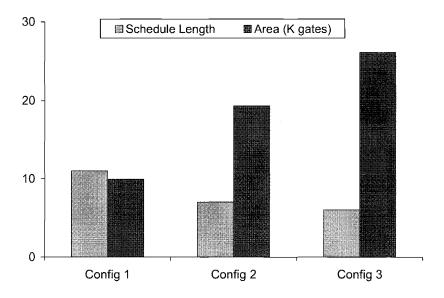

| E.8  | Instruction-set exploration                                 | 166 |

## **List of Tables**

| 3.1 | Specification validation time for different architectures       | 45  |

|-----|-----------------------------------------------------------------|-----|

| 3.2 | Summary of property violations during DSE                       | 48  |

| 3.3 | Validation of in-order execution by two frameworks              | 61  |

| 4.1 | Processor-memory features of different architectures. R4K: MIPS |     |

|     | R4000, SA: StrongArm, 56K: Motorola 56K, c5x: TI C5x, c6x:      |     |

|     | TI C6x, MA: MAP1000A, SC: Starcore, R10: MIPS R10000, MP:       |     |

|     | Motorola MPC7450, U3: SUN UltraSparc IIi, 0.64: Alpha 21364,    |     |

|     | IA64: Intel IA-64                                               | 67  |

| 4.2 | A list of common sub-functions                                  | 71  |

| 5.1 | Validation of the DLX implementation using equivalence checking | 91  |

| 6.1 | Number of test programs in different categories                 | 99  |

| 6.2 | Reduced number of test programs                                 | 100 |

| 6.3 | Test programs for validation of DLX architecture                | 115 |

| 6.4 | Quality of the proposed functional fault model                  | 115 |

| 6.5 | Test programs for validation of LEON2 processor                 | 116 |

| E.1 | The Memory Subsystem Configurations                             | 161 |

| E.2 | Synthesis Results: RISC-DLX vs Public-DLX                       |     |

#### **Preface**

It is widely acknowledged that the cost of validation and testing comprises a significant percentage of the overall development costs for electronic systems today, and is expected to escalate sharply in the future. Many studies have shown that up to 70% of the design development time and resources are spent on functional verification. Functional errors manifest themselves very early in the design flow, and unless they are detected up front, they can result in severe consequences both financially and from a safety viewpoint. Indeed, several recent instances of high-profile functional errors (e.g., the Pentium FDIV bug) have resulted in increased attention paid to verifying the functional correctness of designs. Recent efforts have proposed augmenting the traditional RTL simulation-based validation methodology with formal techniques in an attempt to uncover hard-to-find corner cases, with the goal of trying to reach RTL functional verification closure. However, what is often not highlighted is the fact that in spite of the tremendous time and effort put into such efforts at the RTL and lower levels of abstraction, the complexity of contemporary embedded systems makes it difficult to guarantee functional correctness at the system level under all possible operational scenarios.

The problem is exacerbated in current System-on-Chip (SOC) design methodologies that employ Intellectual Property (IP) blocks composed of processor cores, coprocessors, and memory subsystems. Functional verification becomes one of the major bottlenecks in the design of such systems. A critical challenge in the validation of such systems is the lack of an initial golden reference model against which implementations can be verified through the various phases of design refinement, implementation changes, as well as changes in the functional specification itself. As a result, many existing validation techniques employ a bottom-up approach to design verification, where the functionality of an existing architecture is, in essence, reverse-engineered from its implementation. For instance, a functional model of an embedded processor is extracted from its RTL implementation, and this functional model is then validated in an attempt to verify the functional correctness of the implemented RTL.

xvi PREFACE

If an initial golden reference model is available, it can be used to generate reference models at lower levels of abstraction, against which design implementations can be compared. This "ideal" flow would allow for a consistent set of reference models to be maintained, through various iterations of specification changes, design refinement, and implementation changes. Unfortunately such golden reference models are not available in practice, and thus traditional validation techniques employ different reference models depending on the abstraction level and verification task (e.g., functional simulation or property checking), resulting in potential inconsistencies between multiple reference models.

In this book we present a top-down validation methodology for programmable embedded architectures that complements the existing bottom-up approaches. Our methodology leverages the system architect's knowledge about the behavior of the design through an architecture specification that serves as the initial golden reference model. Of course, the model itself should be validated to ensure that it conforms to the architect's intended behavior; we present validation techniques to ensure that the static and dynamic behaviors of the specified architecture are well formed. The validated specification is then used as a golden reference model for the ensuing phases of the design.

Traditionally, a major challenge in a top-down validation methodology is the ability to generate executable models from the specification for a wide variety of programmable architectures. We have developed a functional abstraction technique that enables specification-driven generation of executable models such as a simulator and synthesizable hardware. The generated simulator and hardware models are used for functional validation and design space exploration of programmable architectures.

This book addresses two fundamental challenges in functional verification: lack of a golden reference model, and lack of a comprehensive functional coverage metric. First, the top-down validation methodology uses the generated hardware as a reference model to verify the hand-written implementation using a combination of symbolic simulation and equivalence checking. Second, we have proposed a functional coverage metric and the attendant task of coverage-driven test generation for validation of pipelined processors. The experiments demonstrate the utility of the specification-driven validation methodology for programmable architectures.

We begin in Chapter 1 by highlighting the challenges in functional verification of programmable architectures, and relating a traditional bottom-up validation approach against our proposed top-down validation methodology. Chapter 2 introduces the notion of an Architecture Description Language (ADL) that can be used as a golden reference model for validation and exploration of programmable architectures. We survey contemporary ADLs and analyze the features required

in ADLs to enable concise descriptions of the wide variety of programmable architectures. We also describe the role of ADLs in generating software tools and hardware models from the specification.

In Chapter 3, we present techniques to validate the ADL specification. In the context of pipelined programmable architectures, we describe methods to verify both static and dynamic behaviors embodied in the ADL, with the goal of ensuring that the architecture specified in the ADL conforms to the system designer's intent, and is consistent and well-formed with respect to the desired architectural properties.

Chapter 4 focuses on the important notion of functional abstraction that permits the extraction of key parameters from the wide range of contemporary programmable architectures. Using this functional abstraction technique, we show how various reference models can be generated for the downstream tasks of compilation, simulation and hardware synthesis. In Chapter 5, we show how the generated hardware models can be used to verify the correctness of the hand-written RTL implementation using a combination of symbolic simulation and equivalence checking.

Chapter 6 introduces the notion of functional fault models and coverage estimation techniques for validation of pipelined programmable architectures. We present specification-driven functional test-generation techniques based on the functional coverage metrics described in the chapter. Finally, Chapter 7 concludes the book with a short discussion of future research directions.

#### **Audience**

This book is designed for graduate students, researchers, CAD tool developers, designers, and managers interested in the development of tools, techniques and methodologies for system-level design, microprocessor validation, design space exploration and functional verification of embedded systems.

#### About the Authors

**Prabhat Mishra** is an Assistant Professor in the Department of Computer and Information Science and Engineering at the University of Florida. He received his B.E. from Jadavpur University, India, M.Tech. from Indian Institute of Technology, Kharagpur, and Ph.D from University of California, Irvine – all in Computer Science. He worked in various semiconductor and design automation companies including Intel, Motorola, Texas Instruments and Synopsys. He received the Outstanding Dissertation Award from the European Design Automation Association

xviii PREFACE

in 2005 and the CODES+ISSS Best Paper Award in 2003. He has published more than 25 papers in the embedded systems field. His research interests include design and verification of embedded systems, reconfigurable computing, VLSI CAD, and computer architecture.

**Nikil Dutt** is a Professor in the Donald Bren School of Information and Computer Sciences at the University of California, Irvine. He received a Ph.D. in Computer Science from the University of Illinois at Urbana-Champaign in 1989. He has been an active researcher in design automation and embedded systems since 1986, with four books, more than 200 publications and several best paper awards. Currently, he serves as Editor-in-Chief of ACM TODAES and as Associate Editor of ACM TECS. He has served on the steering, organizing, and program committees of several premier CAD and embedded system related conferences and workshops. He serves on the advisory boards of ACM SIGBED and ACM SIGDA, and is Vice-Chair of IFIP WG 10.5. His research interests include embedded systems design automation, computer architecture, optimizing compilers, system specification techniques, and distributed embedded systems.

### **Acknowledgments**

This book is the result of many years of academic research work and industrial collaborations. We would like to acknowledge our sponsors for providing us the opportunity to perform the research. This work was partially supported by NSF (CCR-0203813, CCR-0205712, MIP-9708067), DARPA (F33615-00-C-1632), Motorola Inc. and Hitachi Ltd.

This book has the footprints of many collaborations. We would like to acknowledge the contributions of Dr. Magdy Abadir, Jonas Astrom, Dr. Peter Grun, Ashok Halambi, Arun Kejariwal, Dr. Narayanan Krishnamurthy, Dr. Mahesh Mamidipaka, Prof. Alex Nicolau, Dr. Frederic Rousseau, Prof. Sandeep Shukla, and Prof. Hiroyuki Tomiyama. We are also thankful to all the members of the ACES laboratory at the Center for Embedded Computer Systems for interesting discussions and fruitful collaborations.

# Part I Introduction to Functional Verification

#### **INTRODUCTION**

#### 1.1 Motivation

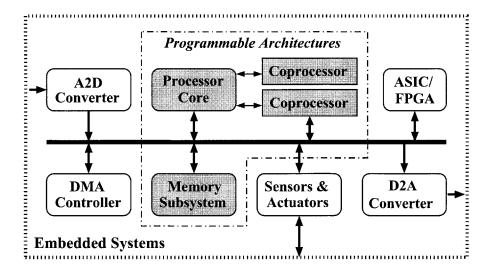

Computing is an integral part of daily life. We encounter two types of computing devices everyday: desktop based computing devices and embedded systems. Desktop based systems encompass traditional computers including personal computers, notebook computers, workstations and servers. Embedded systems are ubiquitous: they run the computing devices hidden inside a vast array of everyday products and appliances such as cell phones, toys, handheld PDAs, cameras, and microwave ovens. Both types of computing devices use programmable components such as processors, coprocessors and memories to execute the application programs. In this book, we refer these programmable components as *programmable embedded architectures* (*programmable architectures* in short). Figure 1.1 shows an example embedded system that contains programmable components as well as application specific hardwares, interfaces, controllers and peripherals.

#### 1.1.1 Growth of Design Complexity

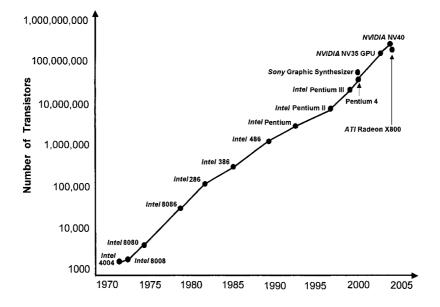

The complexity of the programmable architectures is increasing at an exponential rate. There are two factors that contribute to this complexity growth: technology and demand. First, there is an exponential growth in the number of transistors per integrated circuit, as characterized by Moore's Law [32]. Figure 1.2 shows that Intel processors followed the Moore's law in terms of doubling transistors in every couple of years. This trend is not limited to only high-end general purpose microprocessors. Exponential growth in design complexity is also present in application specific embedded systems. For example, Figure 1.2 also shows the dramatic increase of design complexity for various system-on-chip (SOC) architectures in last few years.

The technology has enabled an exponential increase in computational capacity, which fuels the second trend: the realization of ever more complex applications in the domains of communication, multimedia, networking, and entertainment. For example, the volume of Internet traffic (data movement) is growing exponentially. This would require increase in computation power to manipulate the data. The need for computational complexity further fuels the technological advancement in terms of design complexity.

Figure 1.1: An example embedded system

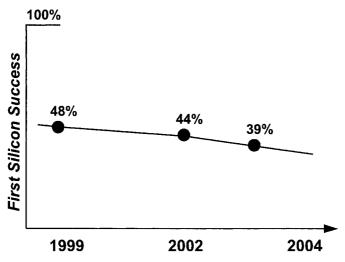

However, the complexity of designing and verifying such systems is also increasing at an exponential rate. Figure 1.3 shows a recent study on the number of first silicon re-spins of system-on-chip (SOC) designs in North America [33]. Almost half of the designs fail the very first time. This failure has tremendous impact on cost for two reasons. First, the delay in getting the working silicon drastically reduces the market share. Second, the manufacturing (fabrication) cost is extremely high. The same study also concluded that 71% of SOC re-spins are due to logic bugs (functional errors).

#### 1.1.2 Functional Verification - A Challenge

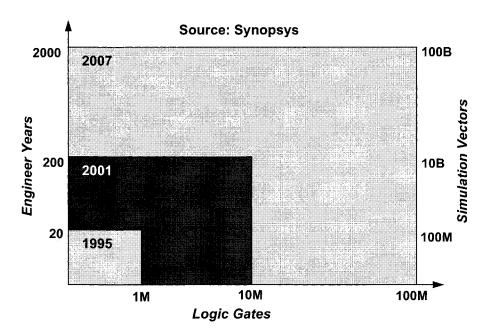

Functional verification is widely acknowledged as a major bottleneck in design methodology: up to 70% of the design development time and resources are spent on functional verification [119]. Recent study highlights the challenges of func-

1.1. MOTIVATION 5

tional verification: Figure 1.4 shows the statistics of the SOC designs in terms of design complexity (logic gates), design time (engineer years), and verification complexity (simulation vectors) [33]. The study highlights the tremendous complexity faced by simulation-based validation of complex SOCs: it estimates that by 2007, a complex SOC will need 2000 engineer years to write 25 million lines of register-transfer level (RTL) code and one trillion simulation vectors for functional verification.

Figure 1.2: Exponential growth of number of transistors per integrated circuit

A similar trend can be observed in the high-performance microprocessor space. Figure 1.5 summarizes a study of the pre-silicon logic bugs found in the Intel IA32 family of microarchitectures. This trend again shows an exponential increase in the number of logic bugs: a growth rate of 300-400% from one generation to the next. The bug rate is linearly proportional to the number of lines of structural RTL code in each design, indicating a roughly constant density [11].

Simple extrapolation indicates that unless a radically new approach is employed, we can expect to see 20-30K bugs designed into the next generation and 100K in the subsequent generation. Clearly – in the face of shrinking time-to-markets – the amount of validation effort rapidly becomes intractable, and will

significantly impact product schedules, with the additional risk of shipping products with undetected bugs.

#### Source: 2002 Collett International Research and Synopsys

Figure 1.3: North America re-spin statistics

The next obvious question is - where do all these bugs come from? An Intel report summarized the results of a statistical study of the 7855 bugs found in the Pentium 4 processor design prior to initial tapeout [11]. The major categories, amounting to over 75% of the bugs analyzed, were [11]:

- Careless coding (12.7%) this includes typos and cut-and-paste errors.

- Miscommunication (11.4%) these errors are due to communication gap.

- Microarchitecture (9.3%) flaws or omissions in the definition.

- Logic/Microcode changes (9.3%) errors due to design changes to fix bugs.

- Corner cases (8%)

- Power down issues (5.7%) errors due to extensive clock gating features.

- Documentation (4.4%) bugs due to incorrect/incomplete documentation.

- Complexity (3.9%) bugs specifically due to microarchitectural complexity.

- Random initialization (3.4%) bugs due to incorrect state initialization.

1.1. MOTIVATION 7

- Late definition (2.8%) bugs due to late addition of new features.

- Incorrect RTL assertions (2.8%)

- Design mistake (2.6%) incorrect implementation errors.

Figure 1.4: Complexity matters

Although "complexity" is ranked eighth on the list of bug causes, it is clear that it contributes to many of the categories listed above. More complex microarchitectures need more extensive documentation to describe them; they require larger design teams to implement them, increasing the likelihood of miscommunication between team members; and they introduce more corner cases, resulting in undiscovered bugs. Hence, microarchitectural complexity is the major contributor of the logic bugs.

Typically, there are two fundamental reasons for so many logic bugs: lack of a golden reference model and lack of a comprehensive functional coverage metric. First, there are multiple specification models above the RTL level (functional model, timing model, verification model, etc.). The consistency of these models is a major concern due to lack of a golden reference model. Second, the design verification problem is further aggravated due to lack of a functional coverage metric

that can be used to determine the coverage of the microarchitectural features, as well as the quality of functional validation. Several coverage measures are commonly used during design validation, such as code coverage, finite-state machine (FSM) coverage, and so on. Unfortunately, these measures do not have any direct relationship to the functionality of the design. For example, in the case of a pipelined processor, none of these measures determine if all possible interactions of hazards, stalls and exceptions are verified.

Figure 1.5: Pre-silicon logic bugs per generation

This book presents a top-down validation methodology that addresses the two fundamental challenges mentioned above. We apply this methodology to verify programmable architectures consisting of a processor core, coprocessors, and memory subsystem [110].

#### 1.2 Traditional Validation Flow

Figure 1.6 shows a traditional architecture validation flow. In the current validation methodology, the architect prepares an informal specification of the programmable architectures in the form of an English document. The logic designer implements the modules at the register-transfer level (RTL). The validation effort tries to uncover two types of faults: architectural flaws and implementation bugs. Validation is performed at different levels of abstraction to capture these faults. For example,

architecture-level modeling (*HLM* in Figure 1.6) and instruction-set simulation is used to estimate performance as well as verify the functional behavior of the architecture. A combination of simulation techniques and formal methods are used to uncover implementation bugs in the *RTL design*.

Figure 1.6: Traditional validation flow

Simulation using random (or directed-random) testcases [1, 19, 37, 63, 123] is the most widely used form of microprocessor validation. It is not possible to apply formal techniques directly on million-gate designs. For example, model checking is typically applied on the high-level description of the design (*ABST* in Figure 1.6) abstracted from the RTL implementation [90, 115]. Traditional formal verification is performed by describing the system using a formal language [53, 20, 118, 62, 64, 78, 79]. The specification (*SPEC* in Figure 1.6) for the for-

mal verification is derived from the architecture description. The implementation (*IMPL* in Figure 1.6) for the formal verification can be derived either from the architecture specification or from the abstracted design. In current practice, the validated *RTL design* is used as a golden reference model for future design modifications. For example, when design transformations (including synthesis) are applied on the *RTL design*, the modified design (RTL/gate level) is validated against the golden *RTL design* using equivalence checking.

A significant bottleneck in these validation techniques is the lack of a golden reference model above RTL level. A typical design validation methodology contains multiple reference models depending on the abstraction level and verification activity. The presence of multiple reference models raises an important question: how do we maintain consistency between so many reference models?

#### 1.3 Top-Down Validation Methodology

We propose the use of a single specification to automatically generate necessary reference models. Currently the design methodology for programmable architectures typically starts with an English specification. However, it is not possible to perform any automated analysis or model synthesis on a design specified using a natural language. We propose the use of an Architecture Description Language (ADL) to capture the design specification. Figure 1.7 shows our ADL-driven validation methodology. The methodology has four important steps: architecture specification, validation of specification, executable (reference) model generation, and implementation (RTL design) validation.

- 1. Architecture Specification: The first step is to capture the programmable architecture using a specification language. Although any specification language can be used that captures both structure (components and their connectivity) and behavior (instruction-set description) of the programmable architectures, we use an ADL in our methodology.

- 2. Validation of Specification: The next step is to verify the specification to ensure the correctness of the architecture specified. We have developed validation techniques to ensure that the architectural specification is well formed by analyzing both static and dynamic behaviors of the specified architecture. We present algorithms to verify several architectural properties, such as connectedness, false pipeline and data-transfer paths, completeness, and finiteness [99]. The dynamic behavior is verified by analyzing the instruction flow in the pipeline using a FSM based model to validate several important architectural properties such as determinism and in-order execution in the presence of hazards and multiple exceptions

[105, 96]. The validated ADL specification is used as a golden reference model to generate various executable models such as simulator and hardware implementation.

Figure 1.7: Proposed specification-driven validation methodology

3. Executable Model Generation: A major challenge in a top-down validation methodology is the ability to generate executable models from the specification for a wide variety of programmable architectures including RISC (Reduced Instruction Set Computer), DSP (Digital Signal Processor), VLIW (Very Long Instruction Word), and superscalar architectures. We have developed a functional abstraction approach by studying the similarities and differences of each architectural feature in various architecture domains. Based on our observations we have defined necessary generic functions, sub-functions, and computational environment needed to capture a wide variety of programmable architectures. Our functional abstraction technique enables generation of simulators [102], hardware prototypes [93], and models for property checking [100] from the ADL specification.

**4. RTL Design Validation**: This book explores two validation scenarios using the generated models: design validation using equivalence checking and test generation for functional validation. The generated hardware is used as a reference model for verifying the hand-written implementation (RTL Design) using a combination of symbolic simulation and equivalence checking [106]. To verify that the implementation satisfies certain properties, our framework generates the intended properties and uses a symbolic simulator to perform property checking. Our framework generates synthesizable RTL description of the architecture to enable equivalence checking with the hand-written implementation.

The specification is also used to generate functional test programs based on the functional coverage of pipelined architectures [100]. The generated test programs are used during simulation of the implementation, and complement the tests generated by the existing techniques such as a random test pattern generator. The generated simulator is used to compute the expected outputs for the test programs. Our experimental results demonstrate that the number of test programs generated by our approach to obtain a functional coverage is an order of magnitude less than those generated by random or constrained-random test generation techniques.

#### 1.4 Book Organization

The organization of the book is as follows.

**Chapter 2 [Architecture Specification]:** Describes necessary features of a specification language that can be used in a top-down validation methodology. It uses EXPRESSION ADL as an example to show how to capture processor, coprocessor, and memory architectures.

**Chapter 3 [Validation of Specification]:** Presents the techniques for validating the architecture specification. These techniques verify both static and dynamic behaviors of the specified architecture.

**Chapter 4 [Model Generation]:** Describes automatic generation of models for simulation, hardware generation, and validation for a wide variety of programmable architectures.

**Chapter 5 [Design Validation]:** The generated hardware is used as a reference model for verifying the hand-written RTL implementation using a combination of symbolic simulation and equivalence checking.

**Chapter 6 [Test Generation]:** Presents specification-driven test generation techniques based on functional coverage of the pipelined processor architectures.

**Chapter 7 [Conclusions]:** Contains a summary of the book and a discussion of future research directions.

# Part II Architecture Specification

#### ARCHITECTURE SPECIFICATION

The first step in a top-down validation methodology is to capture the programmable architectures using a specification language. The language should be powerful enough to specify the wide spectrum of contemporary processor, coprocessor, and memory features. On the other hand, the language should be simple enough to allow correlation of the information between the specification and the architecture manual. Specifications widely in use today are still written informally in natural language like English. Since natural language specifications are not amenable to automated analysis, there are possibilities of ambiguity, incompleteness, and contradiction: all problems that can lead to different interpretations of the specification.

Many formal and semi-formal specification languages for describing software and hardware designs have been proposed over the years. The languages range in expressiveness, and their different levels of granularity determine their appropriateness for different applications. This chapter analyzes several types of specification languages and evaluates the suitability of Architecture Description Languages (ADL) in specifying programmable architectures. We use EXPRESSION ADL [5] to illustrate architecture specification using examples. Within this context, it is important to note that this book does not propose a new language or endorse an existing one. The validation techniques presented in this book can use any existing language that captures both structure and behavior of the programmable architectures.

This chapter is organized as follows. Section 2.1 introduces the notion of an architecture description language and surveys the existing ADLs in terms of their specification capabilities. Section 2.2 analyzes different types of languages and evaluates their suitability in specifying programmable architectures. Section 2.3 describes architecture specification using EXPRESSION ADL [5]. Finally, Section 2.4 summarizes the chapter.

#### 2.1 Architecture Description Languages

The phrase "Architecture Description Language" (ADL) has been used in context of designing both software and hardware architectures. Software ADLs are used for representing and analyzing software architectures ([83], [109]). They capture the behavioral specifications of the components and their interactions that comprises the software architecture. However, hardware ADLs capture the structure (hardware components and their connectivity), and the behavior (instruction-set) of processor architectures. In this book the term ADL will refer to hardware architecture description languages.

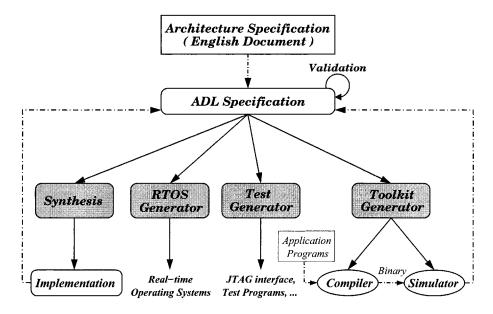

Figure 2.1: ADL-driven exploration and validation of programmable architectures

As embedded systems become ubiquitous, there is an urgent need to facilitate rapid design space exploration (DSE) of programmable architectures. ADLs are used to perform early exploration, synthesis, test generation, and validation of processor-based designs as shown in Figure 2.1. Programmable architectures are captured using an ADL. The ADL specification can be used for generation of a software toolkit including the compiler, assembler, simulator, and debugger. The application programs are compiled and simulated, and the feedback is used to modify the ADL specification with the goal of finding the best possible architecture for the given set of applications. The ADL specification can also be used for gener-

ating hardware prototypes under design constraints such as area, power, and clock speed. Several researchers have shown the usefulness of ADL-driven generation of functional test programs and test interfaces. The specification can also be used to generate device drivers for real-time operating systems [124].

Although, ADL-driven exploration is extensively used in both academia (nML [72], ISDL [31], EXPRESSION [5], Valen-C [6], MIMOLA [117], Sim-nML [132], and LISA [133]), and industry (ARC [10], Axys [42], RADL [15], Target [49], Tensilica [130], LISATek [17], and MDES [80]), to the best of our knowledge, there has not been any effort in validating the ADL specification. It is necessary to validate the ADL specification of the architecture to ensure the correctness of both the architecture specified, as well as the generated software toolkit. Chapter 3 presents specification validation techniques for programmable architectures.

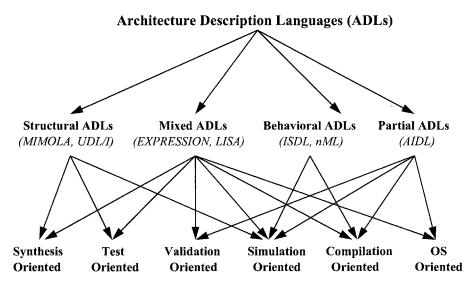

Figure 2.2 shows the classification of architecture description languages (ADLs) based on two aspects: *content* and *objective*. The content-oriented classification is based on the nature of the information an ADL can capture, whereas the objective-oriented classification is based on the purpose of an ADL. Contemporary ADLs can be classified into six categories based on the objective: simulation-oriented, synthesis-oriented, test-oriented, compilation-oriented, validation-oriented, and operating system (OS) oriented.

Figure 2.2: Taxonomy of ADLs

ADLs can be classified into four categories based on the nature of the information: structural, behavioral, mixed, and partial. The structural ADLs capture the

structure in terms of architectural components and their connectivity. The behavioral ADLs capture the instruction-set behavior of the processor architecture. The mixed ADLs capture both structure and behavior of the architecture. These ADLs capture complete description of the structure or behavior or both. However, the partial ADLs capture specific information about the architecture for the intended task. For example, an ADL intended for interface synthesis does not require internal structure or behavior of the processor.

Traditionally, structural ADLs are suitable for synthesis and test-generation. Similarly, behavioral ADLs are suitable for simulation and compilation. It is not always possible to establish a one-to-one correspondence between content-based and objective-based classification. For example, depending on the nature and amount of information captured, partial ADLs can represent any one or more classes of the objective-based ADLs. Recently, many ADLs have been proposed that capture both the structure and the behavior of the architecture. This section presents a brief survey using content-based classification of ADLs. A detailed survey is available in Appendix A.

#### 2.1.1 Behavioral ADLs

nML [72] and ISDL [31] are examples of behavior-centric ADLs. In nML, the processor's instruction-set is described as an attributed grammar with the derivations reflecting the set of legal instructions. nML has been used by the retargetable code generation environment CHESS [22] to describe DSP and ASIP (Application Specific Instruction-set Processor) architectures. In ISDL, constraints on parallelism are explicitly specified through illegal operation groupings. This could be tedious for complex architectures like DSPs which permit operation parallelism (e.g. Motorola 56K) and VLIW machines with distributed register files (e.g. TI C6X). The retargetable compiler system by Yasuura et al. [6] produces code for RISC architectures starting from an instruction-set processor description, and an application described in Valen-C.

Many behavioral ADLs share one common feature: a hierarchical instruction-set description based on attribute grammars [60]. This feature greatly simplifies the instruction-set description by exploiting the common components between operations. However, the lack of detailed pipeline and timing information prevents the use of these languages as an extensible architecture model. Information required by resource-based scheduling algorithms cannot be obtained directly from the description. Also, it is impossible to generate cycle accurate simulators based on the behavioral descriptions without some assumptions on the architecture's control behavior, i.e., an implied architecture template has to be used.

#### 2.1.2 Structural ADLs

MIMOLA [117] and UDL/I [34] are examples of ADLs that primarily capture the structure of the processor: the net-list of the target processor is described in a HDL (Hardware Description Language) like language. One advantage of this approach is that the same description is used for both processor synthesis and code generation. The target processor has a micro-coded architecture. In MIMOLA, the net-list description is used to extract the instruction-set [116, 117], and produce the code generator. UDL/I [34] is used for describing processors at an RT-level on a per-cycle basis. The instruction-set is automatically extracted from the UDL/I description [35], and is then used for generation of a compiler and a simulator.

In general, structural ADLs enable flexible and precise micro-architecture descriptions. The same description can be used for hardware synthesis, test generation, simulation and compilation. However, it is difficult to extract the instruction-set for retargetable compilation.

#### 2.1.3 Mixed ADLs

More recently, languages that capture both the structure and the behavior of the processor, as well as detailed pipeline information have been proposed (EXPRES-SION [5], RADL [15], FLEXWARE [108], MDes [80], and LISA [133]). The main characteristic of LISA is the operation-level description of the pipeline. RADL [15] is an extension of the LISA approach that focuses on explicit support of detailed pipeline behavior to enable generation of production quality cycle-accurate and phase-accurate simulators. FLEXWARE [108] and MDes [80] have a mixed-level structural/behavioral representation. FLEXWARE contains the CODESYN code-generator and the Insulin simulator for ASIPs. The simulator uses a VHDL model of a generic parameterizable machine. The application is translated from the user-defined target instruction-set to the instruction-set of this generic machine. The MDes [80] language used in the Trimaran system is a mixed-level ADL, intended for exploration of parameterized VLIW architectures. Information is broken down into sections (such as format, resource-usage, latency, operation, and register), based on a high-level classification of the information being represented.

The EXPRESSION ADL also follows a mixed-level approach to facilitate DSE. Furthermore, it provides support for specification of novel memory subsystems. It avoids explicit representation of the reservation tables<sup>1</sup> by extracting them from the structural description [88]. The ADL is used to drive the generation of both compiler [4] and simulator [8].

<sup>&</sup>lt;sup>1</sup>Reservation Tables (RTs) have been used to detect conflicts between instructions that simultaneously access the same architectural resource.

#### 2.1.4 Partial ADLs

The ADLs discussed so far captures complete description of the processor's structure, behavior or both. There are many ADLs that captures partial information of the architecture needed to perform specific task. For example, AIDL aims at validation of pipeline behavior such as data-forwarding and out-of-order completion. AIDL is an ADL developed at University of Tsukuba for design of high-performance superscalar processors [129]. In AIDL, timing behavior of pipeline is described using interval temporal logic. AIDL does not support software toolkit generation. However, AIDL descriptions can be simulated using the AIDL simulator.

#### 2.2 ADLs and Other Specification Languages

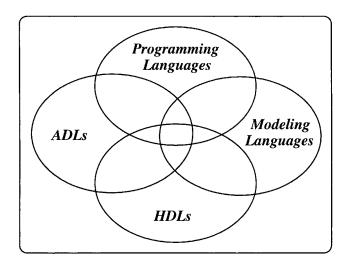

There are various types of specification languages including ADLs, programming languages, hardware description languages, modeling languages, and so on. A natural question is whether an ADL is more suitable for specification of programmable architectures than other languages. In other words, how do ADLs differ from non-ADLs? This section attempts to answer this question. However, it is not always possible to answer the following question: given a language for describing an architecture, what are the criteria for deciding whether it is an ADL or not?

In principle, ADLs differ from programming languages because the latter bind all architectural abstractions to specific point solutions whereas ADLs intentionally suppress or vary such binding. In practice, the architecture is embodied and recoverable from code by reverse engineering methods. For example, it might be possible to analyze a piece of code written in C language and figure out if it corresponds to a *Fetch* unit. Many languages provide architecture level views of the system. For example, C++ language offers the ability to describe the structure of a processor by instantiating objects for the components of the architecture. However, C++ offers little or no architecture-level analytical capabilities. Therefore, it is difficult to describe the architecture at a level of abstraction suitable for early analysis and exploration. More importantly, traditional programming languages are not natural choice for describing architectures due to their inability for capturing hardware features such as parallelism and synchronization.

ADLs differ from modeling languages (such as UML) because the latter are more concerned with the behaviors of the whole rather than the parts, whereas ADLs concentrate on representation of components. In practice, many modeling languages allow the representation of cooperating components and can represent architectures reasonably well. However, the lack of an abstraction would make it harder to describe the instruction-set of the architecture.

Figure 2.3: Commonality between ADLs and non-ADLs

Traditional hardware description languages (HDL), such as VHDL and Verilog, do not have sufficient abstraction to describe architectures and explore them at the system level. It is possible to perform reverse-engineering to extract the structure of the architecture from the HDL description. However, it is hard to extract the instruction-set behavior of the architecture. In practice, some variants of HDLs work reasonably well as ADLs for specific classes of programmable architectures.

There is no clear line between ADLs and non-ADLs. In principle, programming languages, modeling languages, and hardware description languages have aspects in common with ADLs, as shown in Figure 2.3. Languages can, however, be discriminated from one another according to how much architectural information they can capture and analyze. Languages that were born as ADLs show a clear advantage in this area over languages built for some other purpose and later co-opted to represent architectures.

#### 2.3 Specification using EXPRESSION ADL

Our validation framework uses the EXPRESSION ADL [5] to specify processor, coprocessor, and memory architectures. The EXPRESSION ADL follows a mixed-level approach to facilitate specification of a wide range of programmable architectures. We illustrate the use of the EXPRESSION ADL to describe a simple multi-issue architecture consisting of a processor, a coprocessor and a memory subsystem.

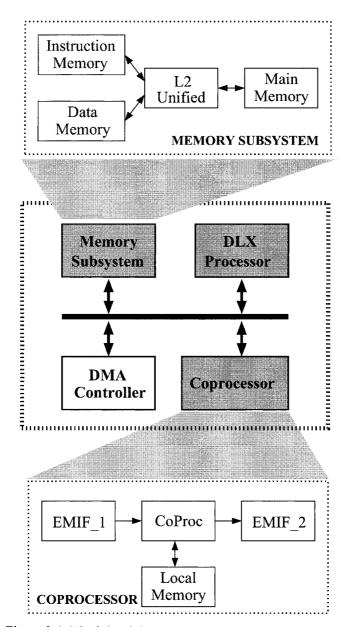

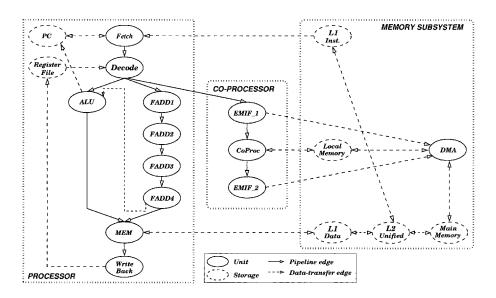

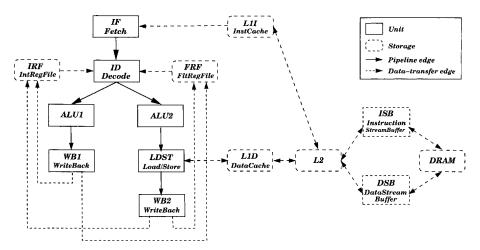

Figure 2.4: Block level description of an example architecture

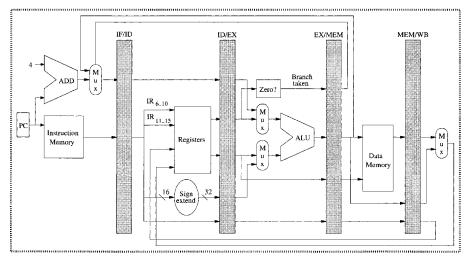

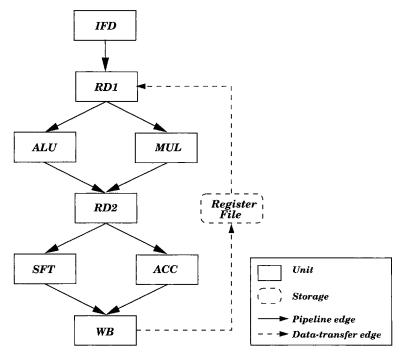

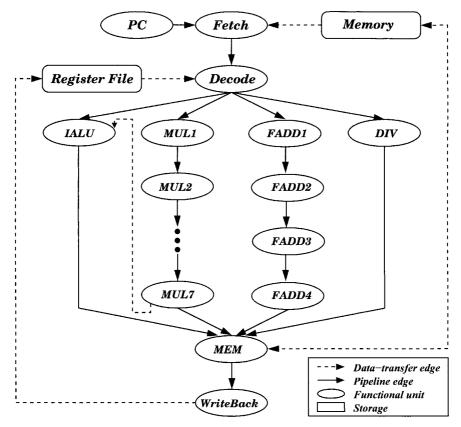

Figure 2.4 shows the block level description of a simple architecture. This level of detail is available in a typical architecture manual. Typically, pipeline level details are available in a micro-architecture manual. For example, Figure 2.4 shows the detailed description of the memory subsystem and the coprocessor. The memory subsystem consists of separate instruction and data memories (L1 cache), a unified L2 memory, and a main memory. The coprocessor consists of three pipeline stages: EMIF\_1 (external memory interface), CoProc, and EMIF\_2. The coprocessor uses it local memory for computations. The data transfer between coprocessor local memory and the main memory is handled by the DMA (direct memory access) controller shown in Figure 2.4. Similarly, Figure 2.5 shows the pipeline level description of the DLX processor shown in Figure 2.4. The DLX processor has five pipeline stages: fetch (IF), decode (ID), execute (EX), memory (MEM), and write back (WB). We have chosen the DLX processor since it has been well studied in academia and there are RTL implementations available that can be used for validation.

Figure 2.5: Pipeline level description of the DLX processor shown in Figure 2.4

The architecture shown in Figure 2.4 can issue up to two operations (an ALU or memory access operation and a coprocessor operation) per cycle. The coprocessor supports vector arithmetic operations. This section briefly describes how to specify the processor, coprocessor, and memory architectures using the EXPRES-SION ADL. The detailed ADL specification of the DLX architecture is available in Appendix B.

# 2.3.1 Processor Specification

This section describes how the EXPRESSION ADL captures the structure and behavior of the DLX processor shown in Figure 2.5.

#### Structure

The structure of a processor can be viewed as a net-list with the components as nodes and the connectivity as edges. Figure 2.6 shows a portion of the EXPRES-SION description of the processor. It describes all the components in the structure: PC, registers, fetch, decode, ALU, MEM, and writeback. Each component has a list of attributes. For example, the ALU unit has information regarding the number of instructions executed per cycle, timing of each instruction, supported opcodes, and so on. The connectivity is established using the description of pipeline and data-transfer paths. Informally, a pipeline path is used to transfer instruction whereas a data-transfer path is used to transfer data. For example,  $\{IF \rightarrow ID \rightarrow EX \rightarrow MEM \rightarrow WB\}$  is a pipeline path, and  $\{WB \rightarrow Registers\}$  is a data-transfer path in Figure 2.5. Section 3.1.1 defines the pipeline and data-transfer paths in detail.

```

# Components specification

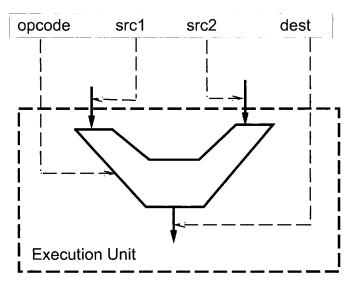

(FetchUnit Fetch

(capacity 2) (timing (all 1))

(opcodes all) (latches ...) ...

)

(ExecUnit ALU

(capacity 1) (timing (add 1) (sub 1) ...)

(opcodes (add sub ...)) (latches ...) ...

)

.....

# Pipeline and data-transfer paths

(pipeline Fetch Decode Execute MEM WriteBack)

(dtpaths (WB Registers) (Registers ALU) ...)

.....

```

Figure 2.6: Specification of the processor structure using EXPRESSION ADL

Figure 2.6 describes the five-stage pipeline as {fetch, decode, execute, memory, writeback}. In this particular case, the execute stage has only one component. In general, the execute stage can have multiple execution paths. Furthermore, each path can contain pipelined or multi-cycle execution units. The ADL specification also includes the description of all the data-transfer paths.

#### Behavior

The EXPRESSION ADL captures the behavior of the architecture as the description of the instruction-set. The behavior is organized into operation groups, with each group containing a set of operations<sup>2</sup> having some common characteristics. For example, Figure 2.7 shows two operation groups. The *aluOps* includes all the operations supported by the *ALU* unit. Similarly, the *memOps* group contains all the operations supported by the *MEM* unit. Each instruction is then described in terms of its opcode, operands, behavior, and instruction format. Each operand is classified either as source or as destination. Furthermore, each operand is associated with a type that describes the type and size of the data it contains. The instruction format describes the fields of the instruction in both binary and assembly. Figure 2.7 shows the description of the *add* and *store* operations.

```

# Behavior: description of instruction-set

( opgroup aluOps (add, sub, ...))

( opgroup memOps (load, store, ...))

.....

( opcode add

(operands (s1 reg) (s2 reg/imm16) (dst reg))

(behavior dst = s1 + s2)

(format 000101 dst(25-21) s1(21-16) s2(15-0))

)

( opcode store

(operands (s1 reg) (s2 imm16) (s3 reg))

(behavior M[s1 + s2] = s3)

(format 001101 s3(25-21) s1(21-16) s2(15-0))

)

```

Figure 2.7: Specification of the processor behavior using EXPRESSION ADL

The ADL also captures the mapping between the structure and the behavior (and vice versa). For example, the *add* and *sub* instructions are mapped to the *ALU* unit, the *load* and *store* instructions are mapped to the *MEM* unit, and so on.

# 2.3.2 Coprocessor Specification

The ADL specification of a programmable coprocessor is similar to the specification of the processor architecture described in Section 2.3.1. This section describes

<sup>&</sup>lt;sup>2</sup>In this book we use the terms operation and instruction interchangeably.

how the ADL captures the structure and behavior of the coprocessor shown in Figure 2.4. To describe the structure of the coprocessor we specify each pipeline stage of the coprocessor along with the processor pipeline as shown in Figure 2.8(a). The coprocessor pipeline has three stages. The *EMIF\_1* stage requests the DMA to transfer the data from the main memory to the coprocessor local memory. The *Co-Proc* stage performs the intended computation using the coprocessor local memory for accessing input operands. Results are stored back in the coprocessor memory. Finally, the *EMIF\_2* requests the DMA to transfer the data from coprocessor memory to main memory. Figure 2.8(a) shows the description of the *CoProc* component. It supports four-cycle vector arithmetic operations.

```

# Components specification

......

( CPunit CoProc

(capacity 1) (timing (vectAdd 4) (vectMul 4))

(opcodes (vectAdd vectMul ...)) ....

)

# Pipeline and data-transfer paths

(pipeline Fetch Decode Execute MEM WriteBack)

(Execute (parallel ALU Coprocessor))

(Coprocessor (pipeline EMIF_1 CoProc EMIF_2))

(dtpaths (EMIF_1 DMA) (EMIF_2 DMA) ...)

.....

```

(a) Structure

```

# Behavior: description of instruction-set

( opgroup cpOps

(vectAdd, vectMul, ...)

)

.....

( opcode vectMul

(operands (s1 mem) (s2 mem) (dst mem) (length imm) )

(behavior dst = s1 * s2)

)

```

,

Figure 2.8: Coprocessor specification using EXPRESSION ADL

(b) Behavior

The behavior of the coprocessor is captured in terms of the operations it supports. For example, Figure 2.8(b) shows the description of a vectMul operation. Unlike normal instructions whose source and destination operands are of type register (except load/store), here source and destination operands are of type memory. The s1 and s2 fields refer to the starting addresses of two source operands for the multiplication. Similarly dst refers to the starting address of the destination operand. The length field refers to the vector length of the operation that has immediate data type.

# 2.3.3 Memory Subsystem Specification

In order to explicitly describe the memory architecture in EXPRESSION, we need to capture both structure and behavior of the memory subsystem. The memory structure refers to the organization of the memory subsystem containing memory modules and the connectivity among them. The behavior refers to the memory subsystem instruction-set.

```

# Storage section

( DCache L1Data

(wordsize 64) (linesize 8) (associativity 2)

(num_lines 1024) (replacement LRU) (latency 1) ...

)

( ICache L1Inst (latency 1) ...)

( DCache L2 (latency 5) ...)

( DRAM MainMemory (latency 50) ...)

# Pipeline and data-transfer paths

(dtpaths (L1Data L2) (L1Inst L2) (L2 MainMemory) ...)

```

(a) Structure

```

# Behavior: description of instruction-set

( opcode load_miss

(operands (s1 L2) (dst L1Data))

(behavior dst = s1)

)

.....

```

(b) Behavior

Figure 2.9: Memory subsystem specification using EXPRESSION ADL

The memory subsystem structure is represented as a netlist of memory components connected through ports and connections. The memory components are described and attributed with their characteristics (such as cache line size, replacement policy, and write policy). For example, Figure 2.9(a) shows the structure of the memory subsystem shown in Figure 2.4. The specification of the memory structure also includes the description of the memory pipeline and data-transfer paths. The memory subsystem instruction-set represents the possible operations that can occur in the memory subsystem, such as data transfers between different memory modules or to the processor (e.g., load and store) or explicit cache control instructions (e.g., prefetch, replace and refill). For example, Figure 2.9(b) shows an internal memory data transfer operation during a load miss. The *load\_miss* operation represents data refill from L2 cache in the event of a L1 data miss.

# 2.4 Chapter Summary

This chapter surveyed existing ADLs in terms of their capabilities in capturing programmable architectures. Structural ADLs enable flexible and precise microarchitecture descriptions. The same description can be used for hardware synthesis, test generation, simulation and compilation. However, it is difficult to extract instruction-set information for retargetable compilation. Behavioral ADLs simplify the instruction-set description by exploiting the common components between operations. However, the lack of a detailed pipeline and timing information prevents the use of these languages as an extensible architecture model. Mixed ADLs capture both the structure and the behavior of the architecture.

The second part of this chapter described the use of the EXPRESSION ADL in our framework to specify programmable architectures. We described how to capture processor, coprocessor, and memory architectures using the ADL. Appendix C describes how to specify interrupts and exceptions in an ADL. Chapter 3 will present techniques to validate the ADL specification of the architecture.

# VALIDATION OF SPECIFICATION

One of the most important requirements in a top-down validation methodology is to ensure that the specification (reference model) is golden. This chapter presents techniques to validate the static and dynamic behaviors of the architecture specified in an ADL. It is necessary to validate the ADL specification to ensure the correctness of both the architecture specified and the generated executable models including software toolkit and hardware implementation. The benefits of validation are two-fold. First, the process of any specification is error-prone and thus verification techniques can be used to check for correctness and consistency of the specification. Second, changes made to the processor during exploration may result in incorrect execution of the system and verification techniques can be used to ensure correctness of the modified architecture.

One of the major challenges in validating the ADL specification is to verify the pipeline behavior in the presence of hazards and multiple exceptions. There are many important properties that need to be verified to validate the pipeline behavior. For example, it is necessary to verify that each operation in the instruction-set can execute correctly in the processor pipeline. It is also necessary to ensure that execution of each operation is completed in a finite amount of time. Similarly, it is important to verify the execution style of the architecture. These properties are by no means complete to prove the correctness of the specification. Additional properties can easily be added and integrated into our validation framework.

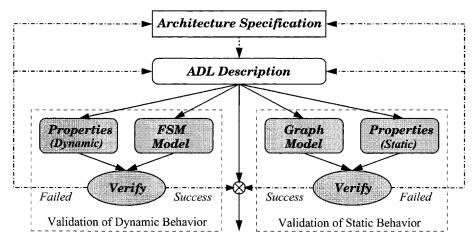

The chapter is organized as follows. Section 3.1 describes the validation techniques to ensure that the static behavior of the pipeline is well-formed by analyzing the structural aspects of the specification using a graph based model. Section 3.2 presents the techniques to verify the dynamic behavior by analyzing the instruction flow in the pipeline using a FSM based model. Section 3.3 presents related work on validation of design specification. Finally, Section 3.4 summarizes the chapter.

## 3.1 Validation of Static Behavior

This section presents an automatic validation framework driven by an ADL. The first step (and only manual step) in the flow is to specify the architecture using an ADL such as EXPRESSION. A novel feature of this approach is the ability to model the pipeline structure and behavior of the processor, co-processor, and memory subsystem using a graph-based model. Based on this model, we present algorithms to ensure that the static behavior of the pipeline is well-formed by analyzing the structural aspects of the specification. Figure 3.1 shows the flow for validating static behaviors. The designer describes the programmable architecture in an ADL. The graph model of the architecture is generated from this ADL description. Several properties are applied to ensure that the architecture is well formed.

Figure 3.1: Validation of pipeline specifications

This section describes three important steps in this methodology. First, it presents a graph-based modeling of processor, memory, and co-processor pipelines. Second, it describes several properties that must be satisfied for valid pipeline specification. Finally, it illustrates validation of pipeline specifications for several realistic architectures.

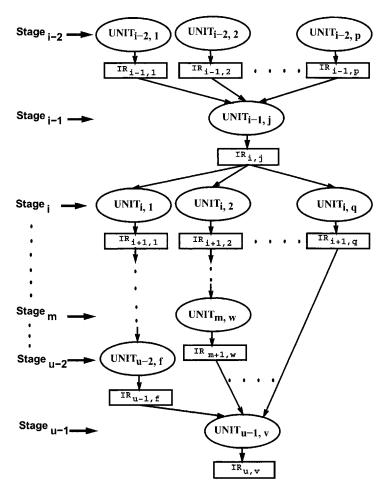

# 3.1.1 Graph-based Modeling of Pipelines

We present a graph-based modeling of architecture pipelines that captures both the structure and the behavior. The graph model presented here can be derived from a pipeline specification of the architecture described in an ADL e.g., EXPRESSION [5]. This graph model can capture processor, memory, and co-processor pipelines for a wide variety of architectures including RISC, DSP, VLIW, and superscalar architectures. In this section, we briefly describe how the graph model captures the structure and behavior of the processor using the information available in the architecture manual.

#### Structure

The structure of an architecture pipeline is based on a block diagram view available in the processor manual, and is modeled as a graph  $G_S = (V_S, E_S)$ , where  $V_S$  denotes a set of components and  $E_S$  consists of a set of edges.  $V_S$  consists of two types of components:  $V_{unit}$  and  $V_{storage}$ .  $V_{unit}$  is a set of functional units (e.g., ALU), and  $V_{storage}$  is a set of storages (e.g., register files).  $E_S$  consists of two types of edges.  $E_{data\_transfer}$  is a set of data-transfer edges, and  $E_{pipeline}$  is a set of pipeline edges. An edge (pipeline or data-transfer) indicates connectivity between two components. A data-transfer edge transfers data between units and storages. A pipeline edge transfers instruction (operation) between two units.

$$V_S = V_{unit} \cup V_{storage}$$

$E_S = E_{data\_transfer} \cup E_{pipeline}$

$E_{data\_transfer} \subseteq \{V_{unit}, V_{storage}\} \times \{V_{unit}, V_{storage}\}$

$E_{pipeline} \subseteq V_{unit} \times V_{unit}$

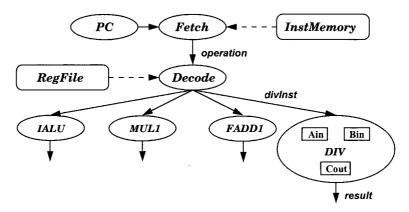

For illustration, we use a simple multi-issue architecture consisting of a processor, a co-processor and a memory subsystem. Figure 3.2 shows the graph-based model of this architecture that can issue up to three operations (an ALU operation, a floating-point addition operation, and a coprocessor operation) per cycle. Figure 3.2 is obtained from Figure 2.4 by adding a four-stage floating point adder (FADD) and a feedback path from the FADD pipeline to the ALU pipeline. In the figure, oval boxes denote units, dotted ovals are storages, bold edges are pipeline edges, and dotted edges are data-transfer edges. A path from a root node (e.g., Fetch) to a leaf node (e.g., WriteBack) consisting of units and pipeline edges is called a pipeline path. For example, one of the pipeline paths is {Fetch, Decode, ALU, MEM, WriteBack}. A path from a unit to main memory or register file consisting of storages and data-transfer edges is called a data-transfer path. For example, {MEM, L1Data, L2, MainMemory} is a data-transfer path.

Figure 3.2: An example architecture

# **Behavior**

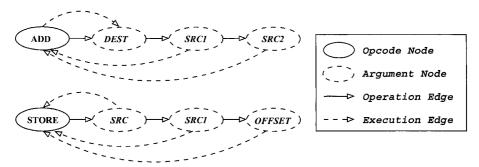

The behavior of the architecture is typically captured by the instruction-set architecture (ISA) description in the processor manual. It consists of a set of operations that can be executed on the architecture. Each operation in turn consists of a set of fields (e.g. opcode, arguments) that specify, at an abstract level, the execution semantics of the operation. We model the behavior as a graph  $G_B = (V_B, E_B)$ , where  $V_B$  is a set of nodes, and  $E_B$  is a set of edges. The nodes represent the fields of each operation, while the edges represent orderings between the fields. The behavior graph  $G_B$  is a set of disjointed sub-graphs, and each sub-graph is called an operation graph (or simply an operation). Figure 3.3 shows a portion of the behavior (consisting of two operation graphs) for the example processor shown in Figure 3.2.

$$egin{array}{lll} V_B &=& V_{opcode} \cup V_{argument} \ E_B &=& E_{operation} \cup E_{execution} \ E_{operation} &\subseteq& V_{opcode} imes V_{argument} \cup V_{argument} imes V_{argument} \ E_{execution} &\subseteq& V_{argument} imes V_{argument} \cup V_{argument} imes V_{opcode} \ \end{array}$$

Nodes are of two types.  $V_{opcode}$  is a set of opcode nodes that represent the opcode (i.e. mnemonic), and  $V_{argument}$  is a set of argument nodes that represent

Figure 3.3: A fragment of the behavior graph

argument fields (i.e., source and destination arguments). In Figure 3.3, the ADD and STORE nodes are opcode nodes, while the others are argument nodes. Edges are also of two types.  $E_{operation}$  is a set of operation edges that link the fields of the operation and also specify the syntactical ordering between them. On the other hand,  $E_{execution}$  is a set of execution edges that specify the execution ordering between the fields. In Figure 3.3, the solid edges represent operation edges while the dotted edges represent execution edges. For the ADD operation, the operation edges specify that the syntactical ordering is opcode (ADD) followed by DEST, SRC1 and SRC2 arguments (in that order), and the execution edges specify that the SRC1 and SRC2 arguments are executed (i.e., read) before the ADD operation is performed. Finally, the DEST argument is written.

#### Mapping between Structure and Behavior

The mapping between the structure and the behavior is captured explicitly in the ADL. This information is available in the architecture manual as mapping between the instruction-set and the functional units. It other words, the manual describes what operations are supported by which functional units in the architecture. We define a set of mapping functions that map nodes in the structure to nodes in the behavior (and vice-versa). The *unit-to-opcode* (opcode-to-unit) mapping is a bi-directional function that maps unit nodes in the structure to opcode nodes in the behavior. The *unit-to-opcode* mappings for the architecture in Figure 3.2 include mappings from Fetch unit to opcodes {ADD, FADD}, ALU unit to opcode ADD, FADD1 unit to opcode FADD etc. The argument-to-storage (storage-to-argument) mapping is a bi-directional function that maps argument nodes in the behavior to storage nodes in the structure. For example, the argument-storage mappings for the ADD operation are mappings from {DEST, SRC1, SRC2} to RegisterFile.

Each functional unit (with read or write ports) supports certain data-transfer operations. These operations can be derived from the above mapping functions. For example, the *Decode* unit of Figure 3.2 supports register read (*regRead*) for ADD and LD opcodes; the *MEM* unit supports data read (*dataRead*) and data write (*dataWrite*) from L1 data cache; the *Fetch* unit supports instruction read (*instRead*) from L1 instruction cache; the *WriteBack* unit supports register write (*regWrite*). Similarly, each storage supports certain data-transfer operations. For example, the *RegisterFile* of Figure 3.2 supports *regRead* and *regWrite*; L1 data cache supports *dataRead* and *dataWrite*, and so on.

# 3.1.2 Validation of Pipeline Specifications

Based on the graph model presented in the previous section, the ADL specification of the architecture pipelines can be validated. In this section, we describe some of the properties used in our framework for validating pipelined architecture specifications.

#### **Connectedness Property**

The connectedness property ensures that each component is connected to other component(s). As pipeline and data-transfer paths are connected regions of the architecture, this property holds if each component belongs to at least one pipeline or data-transfer path.

$$\forall v_{comp} \in V_{\mathcal{S}}, (\exists G_{PP} \in \mathbf{G_{PP}}, \ s.t. \ v_{comp} \in G_{PP}) \lor (\exists G_{DP} \in \mathbf{G_{DP}}, \ s.t. \ v_{comp} \in G_{DP})$$

where  $G_{PP}$  is a set of pipeline paths and  $G_{DP}$  is a set of data-transfer paths.